# **Ultra-Low Jitter Crystal Oscillators (XO)**

### **Features**

- Available at any frequency from 10 MHz to 1000 MHz

- Ultra-Low Jitter (12 KHz to 20 MHz)

- 32 fs at 312.50 MHz

- 34 fs at 491.52 MHz

- Total stability of ±20 ppm

- CML/LVDS/LVPECL/HCSL output formats

- Output Enable/Disable Feature

- < 10 ms start-up time

- No activity dips or micro jumps

- Industry standard 2.5X2.0 mm 6-pin LGA package

- Single 1.8V supply with internal regulator

- Superior power supply immunity

- Temperature range: -40°C to 85°C

- Temperature extended range: -40°C to 105°C

- ESD HBM 2000V, CDM 500V

- Lead free / RoHS compliant

### Applications

- Network Equipment (Optical Modules, routers)

- 100G/200G/400G/800G OTN, Coherent optics

- Storage, switches, servers, NICs, accelerators

- Datacenter

- 3G to 24G SDI broadcast video

- 10G/40G/100G optical ethernet

- 56G/112G PAM4 Clocking

- Test and measurement equipment

# **General Description**

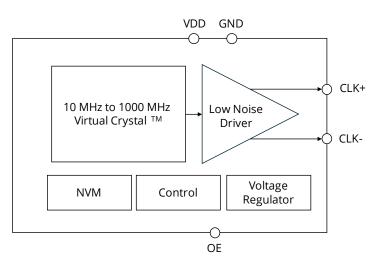

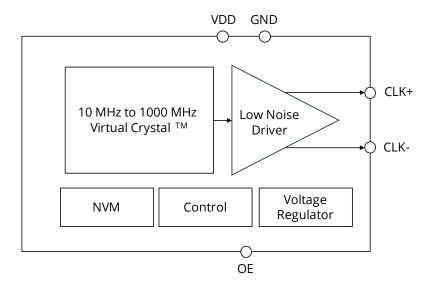

The MS1130 is a crystal oscillator (XO) powered by our Virtual Crystal<sup>™</sup> technology that enables very stable fully programmable multi-GHz clocks with extremely low phase noise.

Adaptive fully autonomous DSP algorithms running in the background continuously monitor and ensure robust and consistent performance over process, voltage and temperature variations.

The devices are factory programmed to provide any frequency between 10 MHz and 1000 MHz with less than 1 ppb resolution.

The MS1130 is manufactured in a high-volume 28 nm CMOS process and represents the most advanced node in the timing industry.

### **Device Information**

| Part Number | Package              | Description      |

|-------------|----------------------|------------------|

| MS1130      | 2.5x2.0 mm 6-pin LGA | Single frequency |

### Figure 1. Functional Block Diagram

# MS1130

### **Single Frequency Device**

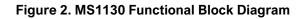

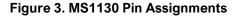

### **Pin Assignment and Pin Description**

| Table 1. MS1130 Pin Description |

|---------------------------------|

|---------------------------------|

| Pin No | Name | Description                |  |  |  |

|--------|------|----------------------------|--|--|--|

| 1      | OE   | Output Enable              |  |  |  |

| 2      | NC   | No Connect                 |  |  |  |

| 3      | GND  | Ground                     |  |  |  |

| 4      | CLK+ | Clock Output               |  |  |  |

| 5      | CLK- | Complementary Clock Output |  |  |  |

| 6      | VDD  | Power Supply               |  |  |  |

# Specifications

#### **Table 2. Electrical Specifications**

Typical values are specified at  $T_A$ = 25°C,  $V_{DD}$ =1.8V unless otherwise specified. All Min and Max limits are specified over the operating temperature range and voltage range with standard termination. A 0.1µF and 10µf bypass capacitor should be connected between VDD and GND pins located close to the device.

| Parameter Symbol | Test Condition/Comment | Min | Тур | Max | Unit |

|------------------|------------------------|-----|-----|-----|------|

|------------------|------------------------|-----|-----|-----|------|

#### **Frequency Range**

| Frequency Range | Fclk | All Output Formats | 10 | 1000 | MHz |

|-----------------|------|--------------------|----|------|-----|

|                 |      |                    |    |      |     |

#### **Frequency Stability**

| Frequency Stability*                                                                                                                                                           | F <sub>STB</sub> | -40°C to 85°C  | -20 |  | 20 | PPM |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|-----|--|----|-----|--|

| Frequency Stability*                                                                                                                                                           | FSTB             | -40°C to 105°C | -25 |  | 25 | PPM |  |

|                                                                                                                                                                                |                  |                |     |  |    |     |  |

| *Frequency stability includes initial tolerance, voltage tolerance, operating temperature and aging (10 year, +25°C). Aging is estimated from environmental reliability tests; |                  |                |     |  |    |     |  |

#### **Clock Output Jitter Characteristics**

| RMS Phase Jitter<br>(12 KHz – 20 MHz) | Φjitter                                                       | Frequency=312.5 MHz |  | 32 |  | fs |  |

|---------------------------------------|---------------------------------------------------------------|---------------------|--|----|--|----|--|

| Note:                                 |                                                               |                     |  |    |  |    |  |

| Phase jitter measured                 | Phase jitter measured on Agilent 5052B Signal Source Analyzer |                     |  |    |  |    |  |

#### **Operating Voltage/Temperature Range**

| Supply Voltage    | V <sub>DD</sub> |                                    | 1.71 | 1.8 | 1.89 | V  |

|-------------------|-----------------|------------------------------------|------|-----|------|----|

|                   | _               | Industrial Temperature             | -40  |     | 85   | °C |

| Temperature Range | TA              | Extended Industrial<br>Temperature | -40  |     | 105  | °C |

### **Current Consumption**

|                |                 | LVDS Output       | 80 | 100 | mA |

|----------------|-----------------|-------------------|----|-----|----|

| Supply Current | I <sub>dd</sub> | (Output Enabled)  |    |     |    |

|                |                 | All Other Outputs | 90 | 110 | mA |

|                |                 | (Output Enabled)  | 00 |     |    |

|                |                 | Tristate Hi-Z     | 50 | 60  | mA |

|                |                 | (Output Disabled) | 50 | 00  |    |

#### **Input Characteristics**

| Digital Input Levels | VIH              |                                                                                | 0.7XV <sub>DD</sub> |      |                  | V  |

|----------------------|------------------|--------------------------------------------------------------------------------|---------------------|------|------------------|----|

| (OE)                 | VIL              |                                                                                |                     | 0.32 | XV <sub>DD</sub> | V  |

| Output Enable (OE)   | T⊳               | Output Disable Time                                                            |                     |      | 3                | us |

|                      | Τ <sub>Ε</sub>   | Output Enable Time                                                             |                     | 2    | 20               | us |

| Powerup Time         | T <sub>PWR</sub> | Time from 0.9xVDD until<br>output frequency (F <sub>CLK</sub> )<br>within spec |                     | 1    | 10               | ms |

#### **PSRR Characteristics**

| Note: |          |                                                                                    |      |     |

|-------|----------|------------------------------------------------------------------------------------|------|-----|

| PSRR  | PSRRspur | Spurs induced by 50mV<br>power supply ripples (All<br>frequency, all output types) | -100 | dBc |

(1) Measured maximum spur level with 50mVpp sinusoidal signal between 50 kHz and 1 MHz applied on VDD Pin

| Output Duty Cycle                                      | DC                              | All Output Formats | 48  |      | 52  | %  |

|--------------------------------------------------------|---------------------------------|--------------------|-----|------|-----|----|

| Output Rise/Fall Time<br>(20% to 80% V <sub>PP</sub> ) | T <sub>R</sub> / T <sub>F</sub> | All Output Formats |     | 65   | 100 | ps |

| LVDS Output<br>(AC Mode)                               | Vo                              | Swing (Diff)       | 0.5 | 0.7  | 0.9 | V  |

| LVDS Extended<br>Output<br>(AC Mode)                   | Vo                              | Swing (Diff)       | 0.8 | 1.2  | 1.6 | V  |

| CML Output<br>(AC Mode)                                | Vo                              | Swing (Diff)       | 0.7 | 0.85 | 1   | V  |

| LVPECL Output<br>(AC Mode)<br>Integrated Termination   | Vo                              | Swing (Diff)       | 1.2 | 1.4  | 1.6 | V  |

| HCSL Output<br>Integrated Termination                  | Vo                              | Swing (Diff)       | 1.2 | 1.4  | 1.6 | V  |

#### Output Characteristics

### Table 3. Absolute Maximum Ratings

| Parameter                                                                                                                          | Min  | Max  | Unit |

|------------------------------------------------------------------------------------------------------------------------------------|------|------|------|

| 1.8V Supply Voltage                                                                                                                | -0.3 | 1.98 | V    |

| Digital I/O                                                                                                                        | -0.3 | 1.98 | V    |

| Maximum Operating Temperature                                                                                                      |      | 105  | °C   |

| Storage Temperature                                                                                                                | -55  | 150  | °C   |

| Soldering Temperature                                                                                                              |      | 260  | °C   |

| Junction Temperature                                                                                                               |      | 150  | °C   |

| Note: Stresses that exceed what is listed in this table may cause permanent damage to the device. Exposure to conditions above the |      |      |      |

Note: Stresses that exceed what is listed in this table may cause permanent damage to the device. Exposure to conditions above the recommendations for extended periods of time may affect device reliability.

#### Table 4. Environmental Compliance

| Parameter                                                                         | Test Condition           |

|-----------------------------------------------------------------------------------|--------------------------|

| Mechanical Shock                                                                  | MIL-STD-883, Method 2002 |

| Mechanical Vibration                                                              | MIL-STD-883, Method 2007 |

| Moisture Sensitivity Level (MSL)                                                  | 3                        |

| Note: For additional information not listed, please contact Mixed-Signal Devices. |                          |

#### Table 5. ESD Levels

| Description                                                                                                                                                                                                   | Description         | Specification     | Level |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------|-------|

| HBM <sup>1</sup>                                                                                                                                                                                              | Human Body Model    | JEDEC JS-001      | 2000V |

| CDM <sup>2</sup>                                                                                                                                                                                              | Charge Device Model | JEDEC JESD22-C101 | 500V  |

| Notes:<br>1. 1000V HBM allows safe manufacturing with standard ESD control process – JEDEC document JEP155<br>2. 250V CDM allows safe manufacturing with standard ESD control process – JEDEC document JEP157 |                     |                   |       |

### Table 6. Package Thermal Information

| Package                                                                                                                                                                              | Parameter                             | Symbol          | Value | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------|-------|------|

| Thermal Resistance, Junction to Ambient                                                                                                                                              |                                       | Ø <sub>JA</sub> | 90    | °C/W |

| 2.5mm x 2mm                                                                                                                                                                          | Thermal Resistance, Junction to Board | ØJB             | 40    | °C/W |

| 6 pin LGA                                                                                                                                                                            | S pin LGA Air Flow Condition          |                 | 0     | mps  |

|                                                                                                                                                                                      | Maximum Junction Temperature          |                 |       | °C   |

| Note: The thermal resistance information stated in this table is based on a standard JEDEC PCB condition. The actual thermal resistance varies depending on the customer PCB design. |                                       |                 |       |      |

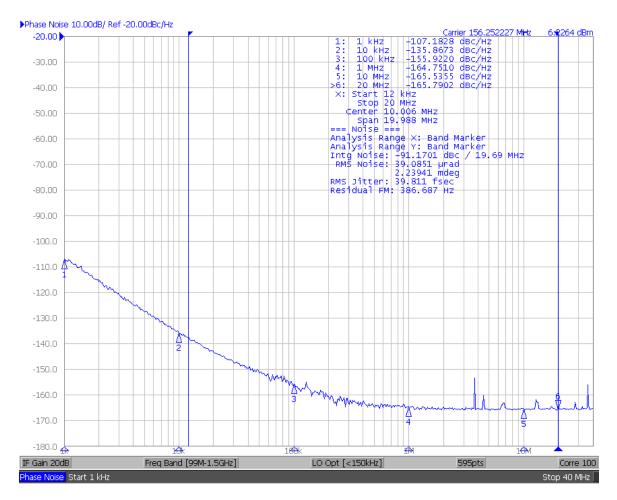

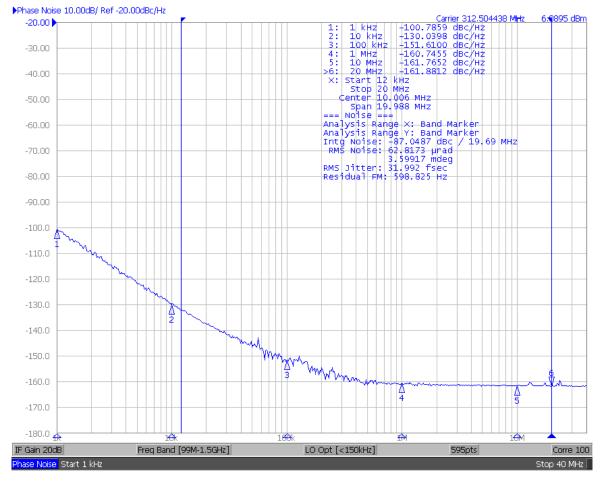

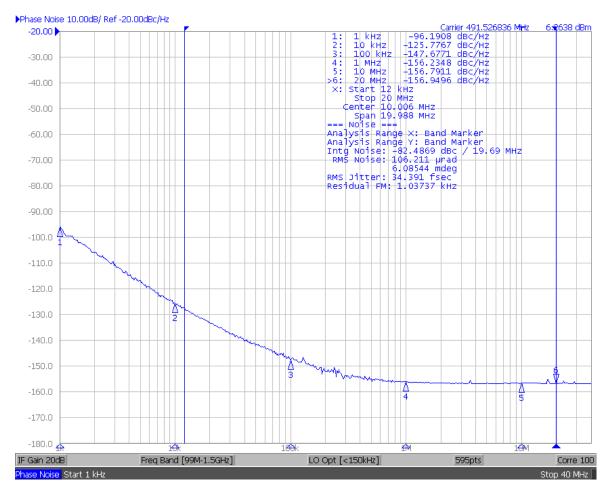

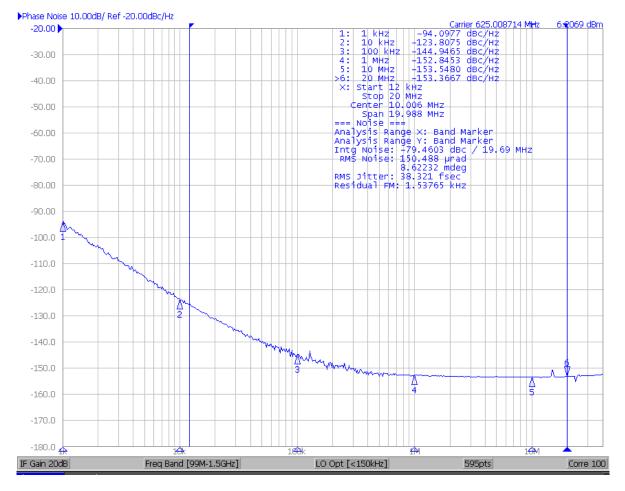

### **Table 7. Typical Output Phase Noise Characteristics**

VDD= 1.8V, T<sub>A</sub> = 25°C, Output Type = CML

| Offset frequency                | 156.25 MHz | 312.50 MHz | 491.52 MHz | 625.00 MHz | Unit   |

|---------------------------------|------------|------------|------------|------------|--------|

| 1 KHz                           | -107       | -101       | -96        | -94        | dBc/Hz |

| 10 KHz                          | -136       | -130       | -126       | -124       | dBc/Hz |

| 100 KHz                         | -156       | -152       | -148       | -145       | dBc/Hz |

| 1 MHz                           | -165       | -161       | -156       | -153       | dBc/Hz |

| 10 MHz                          | -166       | -162       | -157       | -154       | dBc/Hz |

| 20 MHz                          | -166       | -162       | -157       | -154       | dBc/Hz |

| RMS Jitter<br>(12 KHz – 20 MHz) | 39.8 fs    | 31.9 fs    | 34.3 fs    | 38.2 fs    | fs     |

# **Typical Output Measured Phase Noise Plots**

This section shows MS1130 performance plots.

Measurement parameters are: VDD = 1.8 V, TA = 25°C, Output Type = CML.

The plots were captured using an Agilent E5052B Signal Source Analyzer.

Figure 4. Carrier: 156.25 MHz

Figure 5. Carrier: 312.5 MHz

Figure 6. Carrier: 491.52 MHz

Figure 7. Carrier: 625 MHz

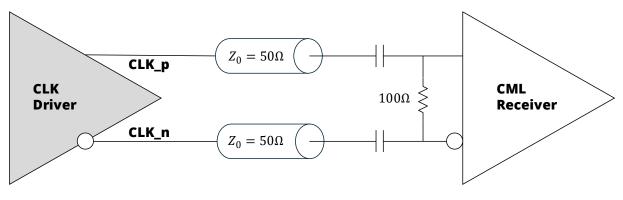

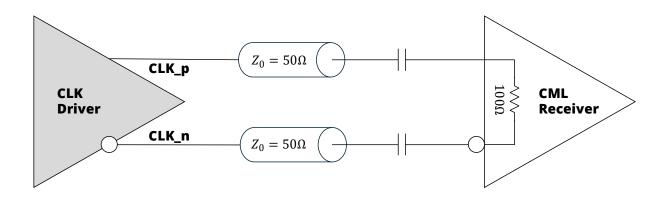

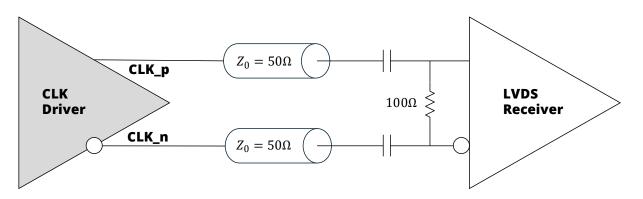

# **Output Terminations**

Figure 8. AC-Coupled CML

Figure 9. AC-Coupled CML (Receiver Termination)

Figure 10. AC-Coupled LVDS

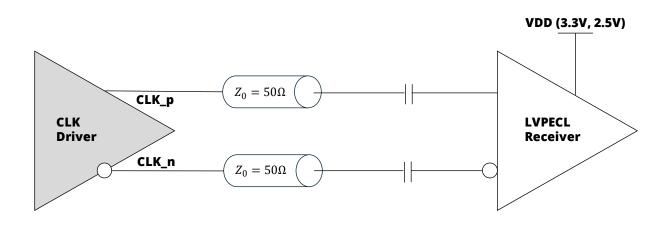

Figure 11. AC-Coupled LVPECL (Integrated Termination)

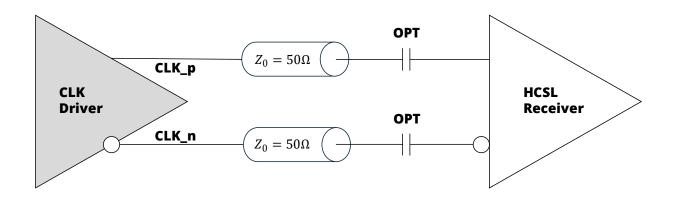

Figure 12. HCSL (Integrated Termination)

# **Packaging Information**

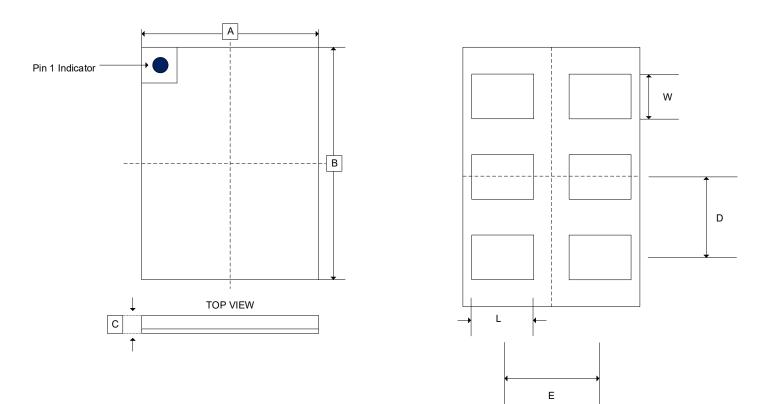

Figure 13 shows the MS1130 packaging drawing.

#### Figure 13. MS1130 Packaging Drawing (2.5X2.0 mm)

| Table 8 | . MS1130 | Packaging | Dimensions |

|---------|----------|-----------|------------|

|---------|----------|-----------|------------|

| Dimensions             | Min      | Nom      | Max  |

|------------------------|----------|----------|------|

| A                      |          | 2.00 BSC |      |

| В                      |          | 2.50 BSC |      |

| С                      | 0.903    | 0.96     | 1.1  |

| L                      | 0.55     | 0.60     | 0.65 |

| W                      | 0.35     | 0.40     | 0.45 |

| D                      | 0.85 BSC |          |      |

| E                      | 1 BSC    |          |      |

| Package Edge Tolerance | 0.1      |          |      |

| Mold Flatness          | 0.2      |          |      |

| Coplanarity            | 0.08     |          |      |

Note: All dimensions are in millimeters

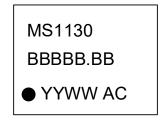

# **Packaging Land Pattern**

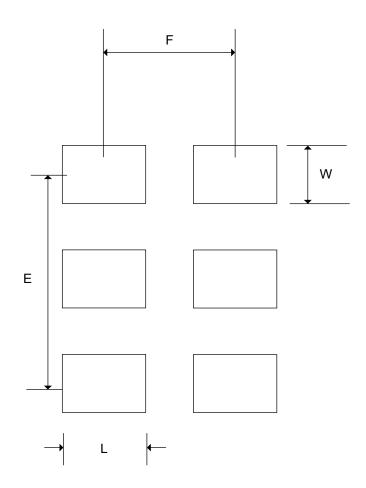

Figure 14 shows the MS1130 PCB land pattern. Note: All dimensions are in millimeters

| Table 9. MS1130 Packagir | ng Land Pattern Dimensions |

|--------------------------|----------------------------|

|                          |                            |

| Dimensions | Length |

|------------|--------|

| L          | 0.75   |

| W          | 0.55   |

| E          | 1.7    |

| F          | 1      |

# **Device Top Marking**

Figure 15. MS1130 Device Top Marking Showing Pin 1

| Line | Position | on Description                     |  |

|------|----------|------------------------------------|--|

| 1    | 1        | Product Marking                    |  |

| 2    | 1-5      | Lot Number                         |  |

| 2    | 6-7      | Wafer Number                       |  |

|      |          | Lot Trace Code                     |  |

|      | 1        | Pin 1 Orientation Mark (Dot)       |  |

| 3    | 2-3      | Year (last two digits of the year) |  |

|      | 4-5      | Calendar Work Week Number (1-53)   |  |

|      | 7-8      | Assembly Code                      |  |

#### Table 10. MS1130 Device Marking Legend

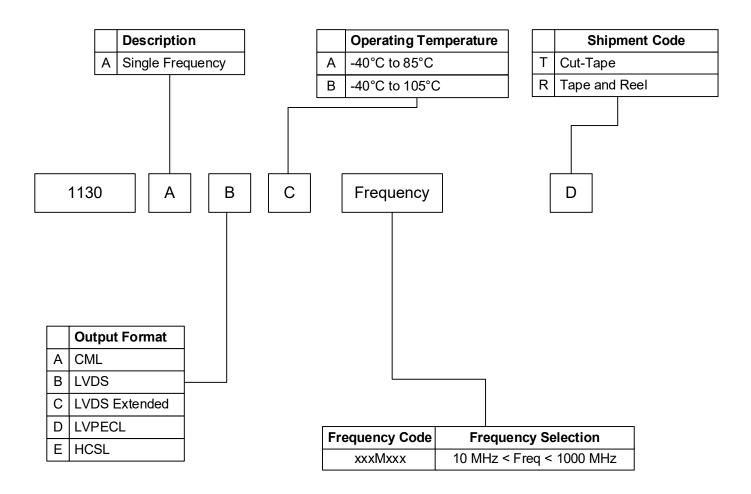

# **Part Ordering Information**

Figure 16 shows a logic tree for ordering each of the available parts.

Figure 16. MS1130 Part Ordering Information

#### IMPORTANT NOTICE AND DISCLAIMER

MIXED-SIGNAL DEVICES INC. PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

Mailing Address: Mixed-Signal Devices Inc, 2 Venture, Suite 300, Irvine, California 92618, USA Copyright © 2024.